I2C Serial Protocol

The following article will provide an overview of the I²C serial protocol. Please, take a look to the article “I2C - Real Time Clock (RTC) DS1307 - Write/Read” on my blog to see a practical approach using the Texas Instrument ARM base LaunchPad Evaluation Kit TM4C123G with a Real Time Clock (RTC) (DS1307) to interact with & better understand the I2C interface.

The I²C Protocol

Inter-Integrated Circuit, or I²C, is a synchronous, half-duplex bi-directional, serial communication interface used for short-distance communication between a master (or multiple masters) and a single or multiple slave device.

An example of a master could be a microcontroller and other IC peripheral’s such as EEPROM, ADC, Temp. sensor, shift register and similar could be the slave. Another microcontroller can act as a slave as well.

INTERFACE

The physical I2C interface consists of only two wires to transmit data between devices:

Note: The Master is the one which initiates a communication, generates a clock and terminates the communication. The Slave is the one which is handled by the master and acts according to the master command.

There needs to be a third wire which is just the ground or 0 volts. There may also be a V 5+ wire if power is being distributed to the devices. Both SDA and SCL lines must be connected to VCC through a pull-up resistor. Why? → Explained Next.

Pull-up Resistors

In many digital communication buses, such as I²C, the signal lines are designed as open-drain (or open-collector). This means that any device connected to the bus—master or slave—can pull the line low (toward ground) but cannot drive it high. When a device is not actively pulling the line low, the line is effectively “floating.”

To ensure that the line reaches a known high voltage level when released by all devices, a pull-up resistor is connected between the line and the supply voltage (commonly 3.3 V or 5 V). This resistor pulls the line high whenever no device is actively driving it low.

For I²C in specific :

- The SCL (clock) and SDA (data) lines of an I²C bus are both open-drain.

- Therefore, each line requires a pull-up resistor to the supply voltage. Typically, one resistor per line is sufficient for the entire bus.

- This ensure signal integrity by providing a defined logic high level.

- It also prevents bus contention, because no device tries to drive the line high, avoiding possible short circuits.

- This configuration enables bidirectional communication, allowing any device on the bus to pull the line low when transmitting, and release it to return high via the pull-up resistor.

| Note: Typical I²C pull-up resistor values range from 2 kΩ to 10 kΩ, depending on bus capacitance, speed, and voltage level

.

General I²C Operation

I²C is a connection-oriented communication protocol with acknowledgement; each transmission is initiated by a START condition and is terminated by STOP condition.

The START and STOP condition.

START condition is generated by a high-to-low change in SDA line when SCL is high.

STOP condition is generated by a low-to-high change in SDA line when SCL is high.

The message could be a device address, register address, or data written to or read from a slave.

The address is to differentiate between other devices that are on the same I²C bus.

The data is the information that could be written or read it from one or multiple registers inside the slave devices.

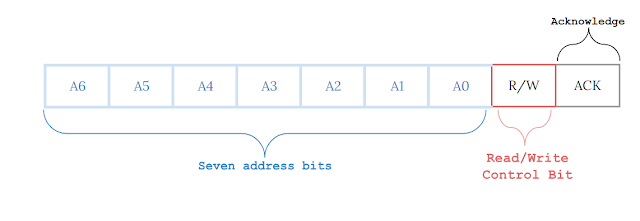

The message, whether it’s a device address, register address, or data it should be framed in 9-bits long.

The MSB of the address is transmitted first.

The first 8-bits are put on the SDA line by the transmitter.

The 9th bit is the acknowledge by the receiver or it may be NACK (Negative Acknowledge)

To allow acknowledgement, the transmitter releases the SDA line during the 9th clock, so the receiver can pull the SDA line low to indicate the ACK. Otherwise, it’s considered a NACK.

Sorce: Understanding the I2C by Texas Instrument

Address Byte Format: 9-bits long

Note: The receiver pulls the SDA line low at the 9th- bit clock pulse to signal an ACK and say it is ready to receive data byte.

Data Byte Format: 9-bits long

Note: When the receiver receives the last data byte and does not need any more data it leaves the SDA line high to signal a NACK and inform the transmitter that it doesn’t need any more data.

START condition + slave address byte + one or more data byte +STOP condition together form a complete data transfer.

Complete Transmission:

Write Sequence

Suppose a master wants to send data to a slave. The sequence is as follows:

Master-transmitter: Sends a START condition.

Master-transmitter: Send the I2C address of the slave-receiver with the R/W bit low for write.

Master-transmitter: Send the internal register number it wants to write to.

Master-transmitter: Sends data to slave-receiver (or bytes, it doesn't have to be just one byte). The master can continue to send data bytes to the slave, and these will normally be placed in the following registers because the slave will automatically increment the internal register address after each byte.

Master-transmitter: Terminates the transfer with a STOP condition.

Note: Every transmission ends with an ACK by the receiver, letting the master know it is ready. by pulling the SDA line low to indicate ACK.

Read Sequence

Suppose a master wants to read data from a slave. Same sequence, it starts with a write but with a few more steps. Here is the sequence:

Master-receiver: Sends a START condition.

Master-receiver: Send the I2C address of the slave-receiver with the R/W bit low for write.

Master-receiver: Send the internal register number it wants to write to.

Master-receiver: Send another start sequence (sometimes called a restart).

Master-receiver: Sends the I2C address again - this time with the R/W bit high for read.

Master-receiver: Read as many data bytes as you wish.

Master-receiver: Terminates the transfer with a STOP condition.

Note: At the end of every byte of data, the master will send an ACK to the slave, letting the slave know that it is ready for more data. Once the master has received the number of bytes it is expecting, it will send a NACK, leaving the SDA line high during the ACK/NACK-related clock period, signaling to the slave to halt communications and release the bus.

Example

Let's say you have data value 0x10100110(A6) and you want to write this value to the slave address 0x1110110 (0x76).

Here’s how the sequence will looks like:

Master-transmitter: Sends a START condition.

SDA line goes from high to low while SCL is high.

Master-transmitter: Send the I2C address of the slave-receiver with the R/W bit low for write.

Master transmit 0x1110110 0 on the bus.

The first 7-bits is the address of the slave.

The 8th-bit is zero (0) to indicate that next data (byte) is going to be written into the slave.

Slave-receiver:

The slave pulls the SDA line low at the 9th clock pulse to signal an ACK; meaning it’s ready to receive data byte.

Master-transmitter: Sends data to slave-receiver (or bytes, it doesn't have to be just one byte).

Master transmit 0x10100110(A6) on the bus.

Slave-receiver:

In the 9th clock pulse the slave leaves the SDA line high to signal an NACK; meaning it receives the last byte of data and does not need any more data.

Master-transmitter: Terminates the transfer with a STOP condition.

SDA line goes from low to high while SCL is high.

I2C clock speed (Update)

For reference... I2C Clock could be one of the following:

Standar Mode 100Kbps

Fast Mode 400Kbps

Fast Plus Mode 1 Mbps

Comments